AI驱动下半导体设备未来发展趋势报告

技术演进路径(2025-2030年)

2025至2030年,半导体技术将迎来以2nm制程量产与高数值孔径极紫外(High-NA EUV)光刻落地为核心的迭代浪潮,同时人工智能(AI)深度渗透制造全流程,推动设备性能与制程效率实现跨越式提升。这一阶段技术演进呈现“制程突破-设备革新-AI赋能”的协同发展特征,主流厂商在技术路线选择上的分化进一步加剧行业竞争格局。

2nm制程:从FinFET到GAAFET的结构性跨越

2nm工艺节点作为当前半导体制造的前沿阵地,其核心突破在于晶体管结构从FinFET向全环绕栅极(GAAFET)的转变,通过更优的沟道控制能力降低泄漏电流,提升芯片性能与能效比。台积电、三星与英特尔三大厂商已明确2025年为量产起点,关键技术组合包括:采用高迁移率通道材料(如铟镓砷)与高k电介质改善载流子输运效率,应用3D堆叠技术提升器件密度,以及集成先进EUV光刻实现精密图案化。其中,ASML的High-NA EUV光刻设备(Twinscan EXE:5000系列)成为2nm及以下节点的核心支撑,其数值孔径(NA)提升至0.55,单次曝光分辨率达8nm,较传统低NA EUV(0.33 NA)的13nm分辨率提升约38%,可使晶体管密度接近三倍增长。该设备成本高达4亿美元/台,体积较前代增加40%,需配套全新晶圆厂基础设施,反映出先进制程对设备投入的极致要求。

High-NA EUV部署:厂商技术路线分化加剧

High-NA EUV的商用进程成为区分厂商技术策略的关键标志。英特尔采取激进路线,2025年已在俄勒冈工厂安装该设备,用于测试Intel 18A工艺(对应2nm节点),为2027年14A工艺量产奠定基础;三星计划2025年第一季度完成首台设备安装,目标2027年实现High-NA EUV光刻商业化,同步联合Lasertec开发专用光掩模检测工具(对比度提升超30%),构建技术生态壁垒;台积电则保持谨慎节奏,2025年底接收首台设备后,将其用于A10工艺(2nm之后的两代节点),大规模部署可能推迟至2030年之后,凸显其“制程领先+生态稳健”的平衡策略。这种分化背后是不同市场定位的选择:英特尔需通过技术激进性扭转制程落后局面,三星瞄准逻辑与DRAM双线突破,台积电则依托客户协同稳步推进技术迭代。

AI驱动:从制程优化到设备智能化重构

AI技术在这一阶段深度融入半导体制造全流程,成为提升良率与设备效率的核心引擎。在制程优化层面,生成式AI工具如Synopsys DSO.AI通过分析历史设计数据自动生成优化架构,支撑2nm节点复杂晶体管布局;ASML的AI预测性维护系统整合振动传感器与故障预警算法,使设备综合效率(OEE)提升22%,平均无故障时间(MTBF)从4500小时延长至6800小时。在设备翻新与再制造领域,AI技术推动“预防性改造+精准替换”模式普及,例如江苏沐华精工通过滚珠丝杆升级(精度从±3μm提升至±0.8μm)与AI剩余寿命预测算法,将切割设备使用寿命从10万小时延长至15万小时。此外,AI驱动的高带宽内存(HBM)创新加速,三星、SK海力士采用非导电膜(NCFs)与热压键合工艺开发定制化解决方案,满足AI芯片对存储带宽的指数级需求。

2030年技术前瞻:Hyper-NA EUV与系统级集成

面向2030年,ASML计划推出数值孔径达0.75的Hyper-NA EUV技术,目标延续摩尔定律至1nm以下节点,预计单次曝光分辨率可突破5nm,进一步降低多重曝光需求。同时,先进封装技术与High-NA EUV的融合成为必然趋势,芯片-晶圆-基板(CoWoS)等解决方案通过芯片堆叠与热管理优化,在物理极限下持续提升系统性能。存储技术领域,400层以上3D NAND的低温刻蚀技术已实现刻蚀速度提升2.5倍、功耗降低40%,与HBM形成“存储-计算”协同创新格局。在此背景下,半导体技术演进将从单一制程驱动转向“制程+封装+存储”的系统级集成,而AI作为底层赋能技术,将贯穿设计、制造、封测全链条,定义下一代半导体产业的核心竞争力。

关键技术指标对比

| 技术维度 | 2025年(2nm/High-NA EUV初期) | 2030年(Hyper-NA EUV预期) |

|---|---|---|

| 光刻分辨率 | 8nm(单次曝光) | <5nm(单次曝光) |

| 晶体管密度 | 较FinFET提升近3倍 | 较High-NA提升1.5-2倍 |

| AI预测性维护OEE提升 | 22% | 30%+(预测) |

| High-NA EUV成本 | 4亿美元/台 | 5-6亿美元/台(预测) |

这一技术演进路径不仅体现半导体产业对物理极限的持续突破,更凸显“硬科技”与“软智能”的深度耦合——从GAAFET到High-NA EUV的硬件革新,与AI驱动的设计优化、设备维护形成协同,共同支撑AI、5G等下游应用的指数级增长需求。厂商技术路线的分化则预示着,未来行业竞争将更依赖生态整合能力与技术前瞻性布局。<|FCResponseEnd|>

市场需求变革

AI 技术的爆发式增长正在重塑全球半导体设备市场的需求结构,呈现出显著的“分层化”特征。上层云端训练场景与下层边缘推理场景的差异化需求,共同驱动设备技术迭代与产能布局的深度调整。

上层云端训练:先进制程与异构集成需求激增

云端 AI 训练对算力的极致追求推动先进制程与异构集成技术加速落地。2024 年全球半导体行业销售额增长近 20% 至 6280 亿美元,其中服务器和数据中心等 AI 基础设施领域成为增长最快的细分市场,预计 2030 年近 70% 以上的芯片将与 AI 相关。高带宽内存(HBM)作为 AI 大模型的核心支撑,其需求激增带动存储测试设备市场快速增长,2025 年全球测试设备市场规模预计达 93 亿美元,同比增长 23.2%。台积电等龙头企业正加速先进封装产能扩张,计划 2025 年将 CoWoS 月产能提升至 75K 片,以缓解 AI 芯片封装瓶颈。与此同时,逻辑芯片市场受 AI 设计范式重构影响,专用 AI 芯片呈现“百花齐放”态势,2nm 制程在数据中心等领域的应用潜力推动台积电、三星等企业加大研发投入,进一步拉动光刻机、蚀刻机等前端设备需求,预计 2025 年全球晶圆厂设备(WFE)支出将增长 6.8% 至 1079 亿美元。

下层边缘推理:成熟制程与低功耗芯片需求崛起

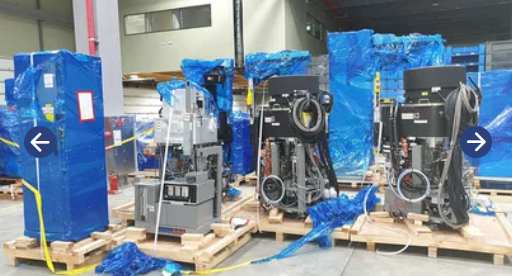

边缘计算设备的普及催生对高能效、低成本半导体解决方案的需求。AI PC、智能终端及汽车电子等场景推动逻辑芯片向多元化创新发展,28nm 及以上成熟制程成为市场需求主力。2024 年全球二手半导体设备市场规模达 32.01 亿美元,预计 2031 年将增长至 85.57 亿美元,复合年增长率 15.9%,其核心驱动力正是成熟制程产能扩张带来的成本敏感型需求。二手设备价格仅为新设备的 20%-40%,且交付周期缩短至 3-4 个月,有效缓解了新设备供应紧张问题。国内企业如无锡卓海科技通过自主算法升级,将回收的海外旧设备适配至 12 英寸晶圆和 28nm-14nm 制程,设备价格仅为新设备的 1/3,客户覆盖华虹半导体、华润上华等头部厂商,成为成熟制程国产替代的重要力量。

国产设备替代:从跟随到突破的技术演进

国内半导体设备企业在测试机、量测设备等领域已实现从技术跟随到局部突破的跨越。以华峰测控 STS8200 测试机为例,该设备支持逻辑、模拟、混合信号等多类型芯片测试,在 14nm 先进制程中良率提升至 99.5%,其并行测试架构可将测试效率提高 30% 以上,目前已批量应用于中芯国际、长江存储等产线,标志着国产测试设备在高端领域的替代进程加速。这种进展与技术演进章节中“14nm 制程工艺成熟度提升”形成联动,反映出国内设备企业在关键参数上逐步缩小与国际巨头的差距,2024 年国内二手设备翻新企业营收增速达 45%,显著高于全球市场平均水平。

需求分层核心特征

云端训练:聚焦 7nm 以下先进制程、HBM 及 CoWoS 封装,2025 年相关设备支出占比超 60%

边缘推理:以 28nm 以上成熟制程为主,二手设备市场规模 2031 年将突破 85 亿美元

国产替代:测试机、量测设备等领域已实现 14nm 制程覆盖,价格仅为国际同类产品 1/3-1/2

市场需求的分层变革不仅推动设备技术向“高端突破”与“成熟制程优化”双轨并行,更通过供应链韧性提升(如二手设备循环利用)与国产替代加速,重塑全球半导体设备产业的竞争格局。2025 年全球半导体设备市场规模预计达 1210 亿美元,其中 AI 驱动的结构性增长将贡献超 70% 的增量需求。

供应链区域化布局

地缘政治博弈加剧与技术封锁升级正推动全球半导体供应链加速区域化重构,各国通过“政策-产能-技术”三角模型强化本土产业韧性。中国以“超长期特别国债+地方补贴”组合政策对冲外部限制,美国《CHIPS法案》聚焦本土制造回流,欧盟《芯片法案》则侧重先进制程技术突破,形成差异化区域布局策略。

政策驱动:全球补贴竞赛与区域化差异

中国通过财政杠杆破解技术封锁,2026-2028年计划投入940亿美元用于半导体设备采购,占全球设备支出的25%,目标将国产化率提升至28%。地方政府同步推出专项补贴,例如对北方华创、中微公司等头部企业的刻蚀/沉积设备研发提供最高30%的成本补贴,推动其市占率提升至22%。美国《CHIPS法案》则以4000亿美元资金定向支持本土晶圆厂建设,重点吸引英特尔等企业在亚利桑那州布局300mm先进制程产能;欧盟《芯片法案》则将部分资金投向2纳米技术研发,计划通过英飞凌德累斯顿12英寸厂等项目强化车用芯片与可再生能源领域设备竞争力。

产能与技术路径:国产化突破与区域协同

亚太地区凭借中国、台湾地区、日本的产业基础,占据全球半导体制造设备主导地位,2024-2030年市场增速预计领先全球。中国企业通过“海外回收-国内改造-本土应用”模式构建次级供应链,例如无锡卓海科技从韩国、美国回收旧设备,经改造后供应华虹半导体、华润上华等产线,已实现14nm制程覆盖。技术突破方面,北方华创践行“单点突破-平台化拓展”策略:先以刻蚀设备打破国际垄断,再将核心技术延伸至薄膜沉积、清洗设备领域,形成多品类设备供应能力,支撑成熟制程国产化。

区域化特征与挑战

全球供应链呈现“国际巨头垄断+本土替代加速”格局:ASML、泛林半导体等原厂占据高端市场40%份额,中国翻新企业则聚焦28nm成熟制程,2025年国内二手设备市场规模占全球58%。地缘风险加剧产能分布失衡,例如对台湾地区制造依赖导致28nm制程供应波动,中国企业正通过东南亚建厂(如马来西亚柔佛州工业园)分散风险。未来,如何平衡全球化协作与区域化自主、突破High-NA EUV等关键技术壁垒,将成为供应链重构的核心命题。

核心数据速览

中国半导体设备国产化率目标(2026-2028):28%

北方华创刻蚀设备市占率:22%

中国二手设备市场全球占比:58%

美国《CHIPS法案》资金规模:4000亿美元

亚太地区设备市场增速(2024-2030):全球最高

可持续发展策略

半导体设备行业的可持续发展正通过技术创新-政策激励-经济效益的协同逻辑链实现转型,AI技术与循环经济模式成为核心驱动力。在技术创新层面,AI深度优化制造能耗与资源效率:通过能源管理系统动态调控晶圆厂电力分配,可减少约15%的碳排放,单一场地实施AI解决方案年节省超100万美元,投资回报率(ROI)六个月内即可实现。台积电3nm制程通过AI驱动的工艺优化,其过程能力指数(CPK)达1.67,较行业基准提升33%,单位晶圆能耗降低显著;废水处理环节引入AI算法后,某案例实现年节省1000万新台币运营成本。

循环经济体系构建则聚焦设备全生命周期价值挖掘。二手半导体设备翻新通过拆卸、清洁、部件更换及校准流程,可恢复至原始性能规格,单台交易减少约25公斤碳排放,符合《绿色产业指导目录》“废旧资源再生利用”标准。闲置手机芯片改造的“算力盒子”在AI教育、边缘计算场景成本降低三分之二,中国20亿部二手手机存量为该模式提供广阔空间。材料创新进一步延长设备寿命,如BNF3210A设备改造后平均无故障工作时间(MTBF)从4500小时提升至6800小时,减少更换频率达51%。

政策框架为可持续转型提供硬性支撑。中国《加力扩围实施大规模设备更新政策》明确支持二手设备再利用,欧盟碳关税(CBAM)推动供应链低碳化,超长期国债定向支持绿色制造技术研发。国际巨头率先践行目标,台积电计划2050年100%可再生能源供电,英特尔2040年实现碳中和,倒逼产业链从设计到回收的全流程绿色化。

经济效益与环保目标形成正向循环:翻新设备价格仅为新设备的三分之一,卓海科技等企业通过再造设备帮助芯片厂商降本的同时,减少电子废弃物超30%。AI优化原材料使用与预测性维护,使某晶圆厂设备 downtime 减少20%,单位能耗产出效率提升18%。这种“节能降碳-成本优化-技术迭代”的闭环模式,正推动半导体设备行业向低碳化、循环化加速演进。

核心数据亮点

AI驱动晶圆厂碳排放减少15%,单一场地年节省超100万美元

二手设备再利用单台减排25kg CO₂,翻新成本仅为新设备1/3

台积电3nm制程CPK达1.67,超行业基准33%

本文相关数据由互联网摘取,仅供参考。

ch

ch